# CS470xx Firmware User's Manual: General Overview and Common Firmware Modules

#### **Contents**

- Document Strategy

- Overview

- Firmware Messaging

- OS Firmware Module

- Audio Manager Firmware Module

- PCM Firmware Module

- Watchdog Timer

- Document Revisions

#### Overview

This document provides a description of the operation of firmware for the CS470xx family of DSPs and attempts to explain frequently used terminology and, at the same time, systematically explains the OS operation and communication for the CS470xx.

This document is a general overview to the family of CS470xx Firmware User's Manuals designated by the general name AN333[X][Y]; where [X] = MPM (matrix processing module), VPM (virtual processing module), PPM (post processing module), and [Y] = A,B,C. The CS470xx family of DSPs does not contain a compressed data decoder.

AN333VPMA

# **Document Strategy**

The CS470xx has been designed with inherently flexibility in terms of firmware usage. Each instance of operation of the CS470xx can potentially use a different mix of DSP firmware, depending on the needs of the end user. The strategy adopted to document the various DSP firmware is based on a single general overview firmware user's manual coupled with an individual application note for each DSP firmware module offered by Cirrus Logic.

The individual application notes each follow as an extension of AN333. These manuals have been named in such a way so as to classify them into one of the following categories:

- Operating system and general overview

- Matrix processing module (MPM)

- Virtual processing module (VPM)

- Post-processing module (PPM)

Delay Module

Dolby Headphone 2

Furthermore, since each classification (such as post-processing module) may contain several associated DSP firmware modules, an incremental letter assignment (such as A, B, C) was given to index each DSP firmware document within a given category. As an example, the table below outlines the general naming conventions for several firmware documents.

**Base Name DSP Firmware Module** Overlay Type Index **Document Reference Number** AN333 General Overview, Operating System (General) AN333 and Common Firmware Modules AN333 Post Processing Module (PPM) а AN333PPMA Crossbar Mixer Module AN333 Matrix Processing Module (MPM) AN333MPMC

С

а

**Table 1-1. Naming Conventions**

For a further breakdown of the available CS470xx firmware modules and their respective application note document numbers, see Section 2.3. Contact your local field applications engineer (FAE) for the latest code updates and availability.

Virtual Processing Module (VPM)

AN333

## 2 Overview

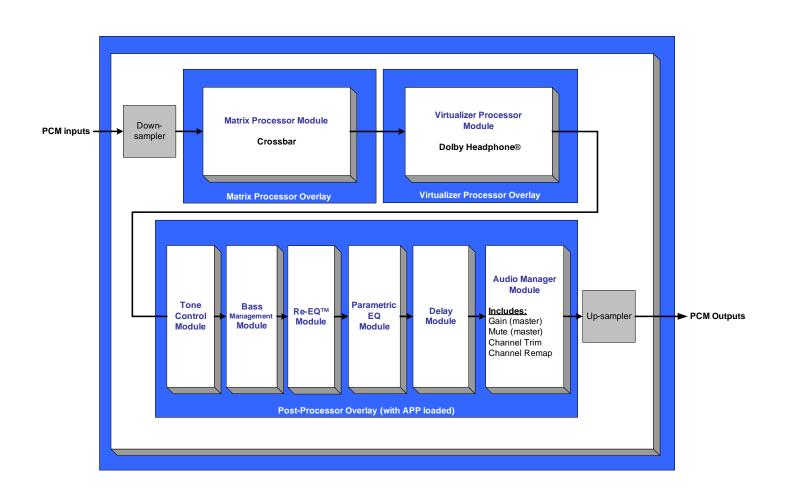

The firmware that runs on this device expects a stereo or multichannel PCM input source. This section describes the overlays.

The DSP program memory is divided into five functional segments called *overlays* that can be thought of as the locations for the firmware modules that are accessed and implemented by the DSP. *Firmware modules* are downloaded into their respective overlays either from internal ROM, or from the host.

- OS Overlay

- Manages the overall operation of the DSP. Also handles host communication, data inputs and outputs, and other critical internal tasks.

- Decoder Overlay

- The decoder overlay on CS47xx only supports the Dolby Digital® decoder in certain memory maps.

- Matrix Processing Overlay

- Performs additional channel generation, upmixing, and downmixing. This overlay is where algorithms such as Dolby® Pro Logic® IIx and Cirrus Original Multichannel Surround 2<sup>™</sup> (COMS-2) reside.

- Virtual Processing Overlay

- Performs stereo virtualizing to simulate multichannel systems, such as Dolby® Audistry®, Dolby Headphone®, and Dolby Virtual Surround™.

- Post-processing Overlay

- This overlay specifically caters to firmware that performs post-processing tasks. It allows the system designer flexibility in tweaking the system for optimal audio performance and effects. This is also the segment in which firmware modules such as the Audio Manager, Bass Manager, Tone Control, Delay, and Parametric EQ Module reside.

# 2.1 Code Image (.uld) Files

Each overlay is a separate code image file (.uld) that is loaded individually into the DSP. To change the functionality of the application, only the overlay of interest needs to be loaded. For example the post-processing overlay can be exchanged from SPP to APP by reloading only the post-processing overlay. This reduces the system response time to user changes, as well as the code image storage requirements.

There are four different memory configurations of the program RAM size, denoted by p2, p4, p6, and p8 (p for program memory; 2, 4, 6, and 8 are the number of kilowords; 1 word = 32 bits). Increasing P RAM decreases Y RAM, while X RAM remains the same. Each overlay is denoted as p2, p4, p6, or p8 in the .uld file name to indicate which memory configuration is used. For example, "ac3\_p2\_xxx.uld".

Memory configuration must be consistent across all overlays (OS, decoder, MPM, VPM, and PPM).

# 2.2 Download Sequence

A standard procedure to download firmware to the DSP follows this structure at system power-up:

## Step 1: Download the firmware OS \_p\*\_\*\*.uld

Automatically fills the OS overlay. (\*2, 4, 6, or 8 for memory map; \*\*device and version)

## Step 2 (optional): Download a matrix processing module

(Examples: Crossbar Mixer, Pro Logic IIx, DTS Neo:6®) Automatically fills the matrix processing overlay.

#### Step 3 (optional): Download a virtual processing module

(Examples: Dolby Headphone, Dolby Virtual Speaker™)

Automatically fills the virtual processing overlay.

## Step 4: Download a post -processor module group

(Examples: SPP, APP)

Automatically fills the post-processing overlay. If SPP or APP is not required, then the bare requirement for this overlay is the Audio Manager module.

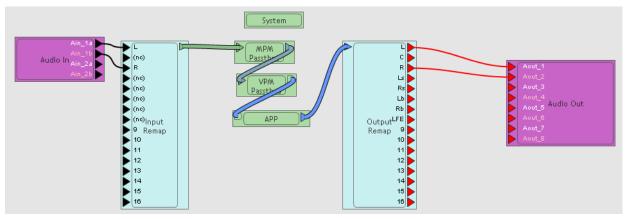

Figure 2-1. Download Sequence

# 2.3 Firmware Modules and Associated Application Notes

Table 2-1. Firmware Module Read and Write Addresses with Associated Application Note Reference

| DSP Firmware Module / (Application Note Name)                | Supported Memory Map(s)<br>(Firmware Version) | Write Request         | Read Request | Read Response         |

|--------------------------------------------------------------|-----------------------------------------------|-----------------------|--------------|-----------------------|

| General                                                      |                                               |                       | •            |                       |

| OS Manager                                                   | 01, 03, 05, 07, 09                            | 0x8100HHHH 0xhhhhhhhh | 0x81C0HHHH   | 0x01C0HHHH 0xhhhhhhhh |

| (AN333)                                                      |                                               |                       |              |                       |

| Matrix Processing Overlay                                    |                                               |                       |              |                       |

| Dolby Pro Logic IIx (AN333MPMA)                              | 01, 07                                        | 0xBF00HHHH 0xhhhhhhhh | 0xBFC0HHHH   | 0x3FC0HHHH 0xhhhhhhhh |

| DTS Neo:6                                                    | 01                                            | 0xB500HHHH 0xhhhhhhhh | 0xB5C0HHHH   | 0x35C0HHHH 0xhhhhhhhh |

| (AN333MPMB)                                                  |                                               |                       |              |                       |

| Crossbar                                                     | 01, 03, 05, 07, 09                            | 0xDB00HHHH 0xhhhhhhhh | 0xDBC0HHHH;  | 0x5BC0HHHH 0xhhhhhhhh |

| (AN333MPMC)                                                  |                                               |                       |              |                       |

| SRS® Circle Surround®                                        | 03, 05                                        | 0xB300HHHH 0xhhhhhhhh | 0xB3C0HHHH   | 0x33C0HHHH 0xhhhhhhhh |

| SRS Circle Surround II                                       |                                               |                       |              |                       |

| SRS Circle Surround Auto                                     |                                               |                       |              |                       |

| (AN333MPMG)                                                  |                                               |                       |              |                       |

| Signal Generator                                             | 01, 03                                        | 0x9A00HHHH 0xhhhhhhhh | 0x9AC0HHHH   | 0x1AC0HHHH 0xhhhhhhhh |

| (AN333MPMH)                                                  |                                               |                       |              |                       |

| Cirrus Original Multichannel Surround 2 (COMS-2)             | 03                                            | 0xD300HHHH 0xhhhhhhhh | 0xD3C0HHHH   | 0x53C0HHHH 0xhhhhhhhh |

| (AN333MPMJ)                                                  |                                               |                       |              |                       |

| Virtual Processor Overlay                                    |                                               |                       |              |                       |

| SRS TruSurround XT®                                          | 01                                            | 0xBA00HHHH 0xhhhhhhhh | 0xBAC0HHHH   | 0x3AC0HHHH 0xhhhhhhhh |

| (AN333VPMH)                                                  |                                               |                       |              |                       |

| Dolby Headphone 2                                            | 01                                            | 0xC000HHHH 0xhhhhhhhh | 0хС0С0НННН   | 0x40C0HHHH 0xhhhhhhhh |

| (AN333VPMK)                                                  |                                               |                       |              |                       |

| Dolby Virtual Speaker 2                                      | 01                                            | 0xC100HHHH 0xhhhhhhhh | 0xC1C0HHHH   | 0x41C0HHHH 0xhhhhhhhh |

| (AN333VPML)                                                  |                                               |                       |              |                       |

| SRS® TruSurround HD4™ Modules (with SRS WOW HD®) (AN333VPMM) | 05                                            | 0xB300HHHH 0xhhhhhhhh | 0хВ3С0НННН   | 0x33C0HHHH 0xhhhhhhhh |

CIRRUS LOGIC®

Table 2-1. Firmware Module Read and Write Addresses with Associated Application Note Reference (Cont.)

| DSP Firmware Module / (Application Note Name)                                     | Supported Memory Map(s)<br>(Firmware Version) | Write Request                                | Read Request | Read Response         |  |

|-----------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|--------------|-----------------------|--|

|                                                                                   | Virtual Processor Over                        | lay (continued)                              | ;_I          |                       |  |

| Cirrus Virtualization Technology (CVT) - Virtualizer Processor Module (AN333VPMN) | 09                                            | 0xC100HHHH 0xhhhhhhhh                        | 0xC1C0HHHH   | 0x41C0HHHH 0xhhhhhhhh |  |

| Post-processing Overlays                                                          |                                               |                                              | •            |                       |  |

| Audio Manager                                                                     | 01, 03, 05, 07, 09                            | 0x8300HHHH 0xhhhhhhhh                        | 0x83c0HHHH   | 0x03c0HHHH 0xhhhhhhhh |  |

| (AN333)                                                                           |                                               |                                              |              |                       |  |

| PCM Manager                                                                       | 01, 03, 05, 07, 09                            | 0x9B00HHHH 0xhhhhhhhh                        | 0х9ВС0НННН   | 0x1BC0HHHH 0xhhhhhhhh |  |

| (AN333)                                                                           |                                               |                                              |              |                       |  |

| Delay                                                                             | 01, 03, 05, 07, 09                            | 0xD900HHHH 0xhhhhhhhh                        | 0xD9C0HHHH   | 0x59C0HHHH 0xhhhhhhhh |  |

| (AN333PPMA)                                                                       |                                               |                                              |              |                       |  |

| Bass Manager                                                                      | 01, 03, 05, 07, 09                            | 0xD700HHHH 0xhhhhhhhh                        | 0xD7C0HHHH   | 0x57C0HHHH 0xhhhhhhhh |  |

| (AN333PPMB)                                                                       |                                               |                                              |              |                       |  |

| Cirrus Band XpandeR (BXR) (AN333PPMC)                                             | 01                                            | 0xE700HHHH 0xhhhhhhhh                        | 0xE7C0HHHH   | 0x67C0HHHH 0xhhhhhhhh |  |

| Cirrus Dynamic Volume Leveler (DVL)                                               | 01                                            | 0xE600HHHH 0xhhhhhhhh                        | 0xE6C0HHHH   | 0x67C0HHHH 0xhhhhhhhh |  |

| (AN333PPMD)                                                                       |                                               | <u>                                     </u> |              |                       |  |

| EQ Module with PEQ and Direct Coefficient Mode (11-bands)                         | 01, 03, 05, 07, 09                            | 0xD500HHHH 0xhhhhhhhh                        | 0xD5C0HHHH   | 0x55C0HHHH 0xhhhhhhhh |  |

| (AN333PPME)                                                                       |                                               |                                              |              |                       |  |

| Tone Control                                                                      | 01, 03, 05, 07, 09                            | 0xD400HHHH 0xhhhhhhhh                        | 0xD4C0HHHH   | 0x54C0HHHH 0xhhhhhhhh |  |

| (AN333PPMF)                                                                       |                                               |                                              |              |                       |  |

| Cinema Re-EQ™                                                                     | 01, 03                                        | 0xDC00HHHH 0xhhhhhhhh                        | 0xDCC0HHHH   | 0x5CC0HHHH 0xhhhhhhhh |  |

| (AN333PPMK)                                                                       |                                               |                                              |              |                       |  |

CIRRUS LOGIC®

Table 2-1. Firmware Module Read and Write Addresses with Associated Application Note Reference (Cont.)

| DSP Firmware Module / (Application Note Name)         | Supported Memory Map(s)<br>(Firmware Version) | Write Request  | Read Request | Read Response |

|-------------------------------------------------------|-----------------------------------------------|----------------|--------------|---------------|

|                                                       | Post-processing Overla                        | ys (continued) |              |               |

| SPP (Standard Post Processing) in DSP Composer Module |                                               |                |              |               |

| Processing Order:                                     |                                               |                |              |               |

| 1. Tone Control                                       |                                               |                |              |               |

| 2. BM                                                 | 01, 03, 05, 07, 09                            | _              | _            | _             |

| 3. Delay                                              |                                               |                |              |               |

| 4. AM                                                 |                                               |                |              |               |

| See individual module application notes.              |                                               |                |              |               |

| APP (Advanced Post Processing) in DSP Composer Mod-   |                                               |                |              |               |

| ule Processing Order:                                 |                                               |                |              |               |

| 1. Tone Control                                       |                                               |                |              |               |

| 2. ReEQ                                               |                                               |                |              |               |

| 3. BM                                                 | 01, 03                                        | _              | _            | _             |

| 4. EQ                                                 |                                               |                |              |               |

| 5. Delay                                              |                                               |                |              |               |

| 6. AM                                                 |                                               |                |              |               |

| See individual module application notes.              |                                               |                |              |               |

# 3 Firmware Messaging

While using the CS470xx, it is necessary to communicate with the DSP in order to control or monitor the various downloaded firmware modules. We refer to this process of communication as firmware messaging. The purpose of this section is to describe the types and formats of these firmware messages. In general, the user can control the firmware module running on the DSP with firmware messaging, and subsequently perform various tasks including the following:

- Configure the module after firmware download (such as kick-starting the DSP)

- Change runtime parameters (such as adjusting the volume or switching Pro Logic II modes)

- Obtain information from the DSP (such as the current state of the firmware registers or data stream information)

#### 3.1 Communication Overview

From a microprogramming point of view, the CS470xx firmware modules can be thought of as blocks of several 32-bit registers (variables) that either control the behavior of the firmware or store information about the state of the firmware at the time of operation. Each register has a unique *index*. Access to the register involves a combination of a specified *opcode* for that firmware module together with the register index. For each firmware module, the following opcodes are available:

- Write Opcode—Issues a command to write to a specific module.

- Read Opcode—Issues a command to read from a specific module.

- Read-response Opcode—Indicates the module and index that have been read.

These available opcodes permit the following types of communication with the CS470xx DSP:

- Writing to the DSP

- Solicited read from the DSP

- Unsolicited read from the DSP

## 3.1.1 Writing to the DSP

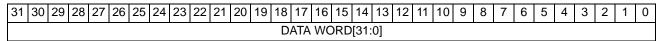

A write session with the CS470xx consists of one 8-byte message from the host to the CS470xx. The write message consists of a 32-bit *command word* followed by a 32-bit *data word* (that is, data to be written to the register). The command word is formed by combining the write opcode for that module with the index of the register that needs to be written. The 32-bit data word is the value of the data intended to fill that register.

Fig. 3-1 shows the format of a write message:

#### Write Command Word:

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 | 15   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0 |

|-------------------------------------------------|---------------------------------------------------------------------|

| OPCODE[31:16]                                   | INDEX[15:0]                                                         |

#### Write Data Word:

Figure 3-1. Write Command and Write Data Words

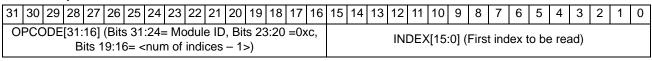

#### 3.1.2 Solicited Read

A solicited read can be thought of as a request to read the contents of a specific register. A solicited read is composed of a 32-bit solicited read-command word, which is a request to read a specific index (register) in a given module or read up to sixteen consecutive indices. The DSP, upon receiving this message, responds by sending back a 32-bit read-response opcode and the requested 32-bit data word(s) contained in each of the indices read.

Fig. 3-2 provides the format of a solicited read message:

#### Read Command Word:

| 31 30 29 28 27 26 25                          | 24 23 22 21 | 20 19 | 18 17 | 16  | 15 14 | 13 | 12  | 11  | 10    | 9    | 8     | 7     | 6     | 5     | 4     | 3   | 2 | 1 | 0 |

|-----------------------------------------------|-------------|-------|-------|-----|-------|----|-----|-----|-------|------|-------|-------|-------|-------|-------|-----|---|---|---|

| OPCODE[31:16] (Bits 31:2<br>0xc, bits 19:16 = |             |       |       | 0 = |       |    | INE | DEX | ([15: | 0] ( | First | t ind | lex t | to be | e rea | ad) |   |   |   |

Figure 3-2. Read Command Data Word

Fig. 3-3 provides the format of a solicited read message:

#### Read-Response Command Word:

#### Read-Response Data Word(s):

Figure 3-3. Read-Response Command and Read-response Data Words

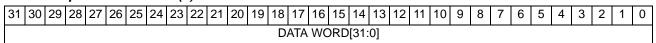

# 3.1.3 Unsolicited Message

The DSP needs to inform the host when the PLL is out of lock or there is a runtime memory allocation error (malloc failure). This type of message is considered an unsolicited message because it was initiated by the CS470xx rather than the host.

This message comes from the CS470xx to indicate a change in the system that must be addressed. The 8-byte unsolicited read messages from the CS470xx consists of a 4-byte read command word, which defines the type of unsolicited message, and an associated 4-byte data word that contains more information describing a system condition. When the IRQ pin for the port being used goes low (SCP1\_IRQ) or PCP\_IRQ), the host senses that an unsolicited message is ready to be read. Every time a message is detected, the host reads out the 8-byte unsolicited read message.

# 4 Operating System (OS) Firmware Module

#### **Unsolicited Read Command Word:**

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 |             |  |  |  |  |  |  |

|-------------------------------------------------|-------------|--|--|--|--|--|--|

| OPCODE[31:16]                                   | INDEX[15:0] |  |  |  |  |  |  |

| Unsolicited Read Data Word:                     |             |  |  |  |  |  |  |

| Unsolicited Read Data Word:                     |             |  |  |  |  |  |  |

DATA WORD[31:0]

Figure 4-1. Unsolicited Read Command and Data Words

Table 4-1 describes the API used to control the OS firmware module. Indices of the Firmware Module can differ in properties that are important to the system firmware programmer.

Variables marked by a '†' can be modified after kick-starting the application. However, variables **not** marked by a '†' must be configured by the system host controller **before** the kick-start message is sent to begin decoding. For these indices, changes after kick-starting the application do not have the desired effect and can potentially cause the application to become unstable.

All indices are reinitialized to the default values after downloading the overlay and soft-resetting the overlay.

Index = 0xHHHH, data value = 0xhhhhhhhh

Write = 0x8100HHHH 0xhhhhhhhh

Read Request = 0x81C0HHHH

Read Response = 0x01C0HHHH 0xhhhhhhhh

## Table 4-1. OS Firmware Manager

| Index  | Variable             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000 | KICKSTART            | Bit 16: 0/1 Disable/enable malloc failure reporting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        |                      | Bit 13: 0/1 Disable/enable continual GPIO updating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|        |                      | Only applicable if Bit 12 is set. If Bit 12 is disabled, audio pins are be available.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|        |                      | Bit 12: 0/1 Disable/enable GPIO updates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        |                      | Bit 9: 0/1 Disable/enable hardware watchdog timer reload.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        |                      | Bit 8: 0/1 Disable/enable hardware watchdog timer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |                      | When Bit 8 is set, the hardware watchdog timer is enabled. When the watchdog timer is enabled, the timer with the initial set value starts decrementing, and when it reaches zero, it stops decrementing and resets the hardware. Every 16 audio samples, there is an option to reload the watchdog timer, controlled by bit 9. If bit 9 is set, a watchdog timer reload does not take place. Otherwise, the counter is reloaded with the set value every 16 audio samples.  Bit 0: Kick-start: Set to 1 to trigger kick-start |

| 0v0001 | IO CONFIC            | Default = 0x00000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x0001 | IO_CONFIG            | See Section 4.2 for the details of this index.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x0002 | OUTPUT_MODE_CONTROL† | Bits 7:4 Dual Mono Mode (valid only if input mode is 0x0000)  0x0 = Stereo Mode => Center out = None                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        |                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|        |                      | Left_out = Left_in Right_out = Right_in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|        |                      | 0x1 = Left Mono => Center_out = Left_in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|        |                      | Left_out = None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |                      | Right out = None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |                      | 0x2 = Right Mono => Center_out = Right_in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        |                      | Left_out = None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |                      | Right_out = None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |                      | 0x3 = Mixed Mono => Center_out = (Lin+Rin)/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        |                      | Left_out = None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |                      | Right_out = None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |                      | For non-zero values (1,2 or 3) in bits 7:4 of the OUTPUT_MODE_CONTROL variable, values in bits 3:0 are ignored.                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |                      | Dual mono mode selection is available only if input mode is 0, that is for dual mono streams.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|        |                      | Bits 3:0 Output Mode (number of speakers present in the system)                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |                      | 0x0 = 2/0 Lt, Rt Dolby Surround compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|        |                      | 0x1 = 1/0 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |                      | 0x2 = 2/0  L/R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|        |                      | If the output mode is set to 0x02 and Dolby decoding is also set, then the output is Lt/Rt or Lo/Ro depending on the setting of the AC3 Manager STEREO_MODE_CONTROL. See AN333DA for more information.                                                                                                                                                                                                                                                                                                                         |

|        |                      | 0x3 = 3/0 L/C/R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |                      | 0x4 = 2/1 L/R/S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |                      | 0x5 = 3/1  L/C/R/S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |                      | 0x6 = 2/2 L/R/Ls/Rs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|        |                      | 0x7 = 3/2 L/C/R/Ls/Rs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|        |                      | 0x8 = 3/3 L/C/R/Ls/Rs/Cs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        |                      | 0x9 = 3/4 L/C/R/Ls/Rs/Sbl/Sbr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|        |                      | 0xA = 2/3 L/R/Ls/Rs/Cs $0xB = 2/4 L/R/Ls/Rs/Cs$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |                      | 0xB = 2/4 L/R/Ls/Rs/Sbl/Sbr<br>Default = 0x00000007                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|        |                      | Default = 0x00000007                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Table 4-1. OS Firmware Manager (Cont.)

| Index         | Variable                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0003        | SAMPLE_RATE†                    | The host must set the sample rate variable to inform firmware modules of the sample rate. Some firmware modules use this information to calculate correct coefficients or use the correct table data. The actual sample rate is determined by the DAO_LRCLK, which can be configured to be master or slave. If the DAO_LRCLK is master, the sample_rate can be set using the DAO clock dividers. See the CS470xx Hardware User's Manual for more information.  Bits 3:0 Sample Rate  0x0 = 48 kHz  0x1 = 44.1 kHz  0x2 = 32 kHz  0x3 = Reserved  0x4 = 96 kHz  0x5 = 88.2 kHz  0x6 = 64 kHz  0x7 = Reserved  0x8 = 24 kHz  0x9 = 22.05 kHz  0xA = 16 kHz  0xB = Reserved  0xC = 192 kHz  0xD = 176.4 kHz  0xE = 128 kHz |

|               |                                 | 0xF = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               |                                 | Default = 0x00000000 (48 kHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x0004-0x0008 | Reserved                        | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x0009        | SOFTBOOT†                       | Bit 4: 1 = Engage low-power mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               |                                 | Bit 0: 0/1 disable/initiate soft boot sequence.  After a soft boot is initiated, the OS sends a 0x00000005 (SOFT_BOOT_ACK) to the host. The host can then use the standard boot protocol to download one or more overlays. After a soft boot is initiated, the OS will respond to boot protocol messages only.  The bit is reset to 0 after the soft boot is complete.  Default = 0x000000000                                                                                                                                                                                                                                                                                                                           |

| 0x000A        | WATCHDOG_CONFIG1                | Specifies the software watch-dog expiry count in terms of timer0 ticks (timer isr counts). This count is decremented in Timer0 ISR and upon reaching zero system is restarted.  Bits 31:0 0 = Disable Software watchdog. <count_value> = Value of count in timer0 ticks to be elapsed before an app_restart.  Default: 0x1000 (corresponds to approximately 4 seconds assuming DSP_CLOCK is 150 MHz and TIMER_RELOAD is 0x249F0).</count_value>                                                                                                                                                                                                                                                                         |

| 0x000B        | TIMER0_RELOAD_COUNT1            | Specifies the value of TIMER0_RELOAD register from which count down to zero begins.  TIMER0_COUNT starts with this value and is decremented every processor cycle and is reloaded back to this value upon reaching zero. Setting this register also sets the frequency of TIMER0 ISR because timer isr fires whenever TIMER0_COUNT reaches zero.  Bits 31:0 <timer_reload_value> Default: 0x249F0 (corresponds to 1 millisecond assuming DSP_CLOCK is 150 MHz).</timer_reload_value>                                                                                                                                                                                                                                    |

| 0x000C        | TIMER_MODULE_COUNT <sup>1</sup> | Specifies the value for frequency of executing timer entry point of modules. The value is specified in terms of timer0 ticks (timer isr counts).  Bits 31:0 <timer_module_count>  Default: 500 (corresponds to half a second assuming DSP_CLOCK is 150 MHz and TIMER_RELOAD is 0x249F0).  Note: Since timer entry point of modules is called from BRICK_ISR thread minimum frequency of occurrence for timer modules is limited to 16/Fs sec (0.33 msec for 48 kHz).</timer_module_count>                                                                                                                                                                                                                               |

| 0x000D-0x003A | Reserved                        | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x003B        | GPIO_D†                         | GPIO data register.  Bits 31:0  Bit[i] corresponds to pin GPIO[i] (i=0,,31).  Both the GPIO_OE and GPIO_MUX must be set to 1 for a particular bit before that bit can be written. Bit 13 and 12 of KICKSTART variable must be set to 1(enabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 4-1. OS Firmware Manager (Cont.)

| Index         | Variable                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x003C        | GPIO_OE                               | GPIO data direction register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               |                                       | Bits 31:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|               |                                       | When Bit[i] is 1, pin GPIO[i] is configured as an output. When Bit[i] is 0, pin GPIO[i] is configured as an input. (i=0,,31).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x003D        | GPIO_MUX                              | GPIO MUX Selector register. Bits 31:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               |                                       | When Bit[i] is 1, pin GPIO[i] is a GPIO function. When Bit[i] is 0, pin GPIO[i] is overwritten by the other function on that pin. Also, when Bit[i] is 0, Bit[i] of the GPIO_D register is not writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0x003E-0x0043 | Reserved                              | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x0044        | PLL_STANDARD_CONFIG                   | Bits 11:4 Reference Clock Frequency is the frequency of clock attached to XTI pin, must be set:  0x00 = 12.288 MHz 0x01 = 24.576 MHz 0x02–0x0F = Reserved 0x10 = 18.432 MHz 0x11 = 27 MHz 0x12–0xFF = Reserved Bits 3:0 DSP core speed: 0x0 = Custom speed. 0x1 = 101 MHz 0x3 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|               |                                       | 0x5 = 152 MHz<br>0x2, 0x4, 0x6-0xF = Reserved<br>Default = 0x00000011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x0045        | PLL_CUSTOM_CONFIG0                    | Bits 31:0 PLL Custom Configuration 0:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               |                                       | 0x00002402 - 11.2896 MHz REF_CLK frequency - 101 Core Speed 0x00002B02 - 11.2896 MHz REF_CLK frequency - 122 Core Speed 0x00002302 - 11.2896 MHz REF_CLK frequency - 130 Core Speed 0x00002002 - 12.288 MHz REF_CLK frequency - 130 Core Speed 0x00001502 - 18.432 MHz REF_CLK frequency - 130 Core Speed 0x80000000 - 24.576 MHz REF_CLK frequency - 130 Core Speed 0x74000000 - 27.000 MHz REF_CLK frequency - 130 Core Speed PLL1_CUSTOM_CONFIG0: For REF_CLK frequencies greater than or equal to 24.576 MHz, setting of fract_in of PLL1 (fract_in is in 1.31 unsigned fractional format, range: 1.000 to 0) VCO_CLK = fract_in * 32 * REF_CLK. PLL1_CUSTOM_CONFIG0: For REF_CLK frequencies less than 24.576 MHz, setting of fb_div of PLL1 (bits 13:8 sets fb_div value and bit 1 sets the additional multiplying factor of 2) VCO_CLK = REF_CLK * fb_div * 2. REF_CLK is the reference clock at XTI pin. |

| 0x0046        | PLL_CUSTOM_CONFIG1                    | Bits 31:0 PLL Custom Configuration 1:  0x00000300 - 101 or 122 Core Speed  0x00000200 - 130 Core Speed  PLL1_CUSTOM_CONFIG1  Setting of OVFS_MUX (bit 12), OVFS_DIV1 (bits 3:0), OVFS_DIV2 (bits 7:4), HCLK_DIV (bits 11:8; other bits are reserved) for the DSP Clock.  OVFS_MUX selects divided VCO_CLK for I2S_OVFS_CLK, else it is REF_CLK.  I2s_OVFS_CLK = VCO_CLK / (2 * (OVFS_DIV1+1) * (OVFS_DIV2+1)) This is the DAO MCLK output used when DAO MCLK is set as Master.  DSP_CLK = VCO_CLK / (2 * (HCLK_DIV+1))                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x0047-0x004E | Reserved                              | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x004F        | SW_NUM_CHANS                          | Number of software audio channels to be supported in OS I/O buffers.  Bits 5:0 Number of channels. Maximum supported is 16.  Default: 0x00000008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x0050-0x0054 | Reserved                              | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0x0055        | MALLOC_SUCCESS_AND_<br>ATTEMPT_COUNTS | Read Only Bits 31:16 Number of successful memory allocations. Bits 15:0 Number of memory allocation attempts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x0056-0x0058 | Reserved                              | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Table 4-1. OS Firmware Manager (Cont.)

| Index   | Variable                 | Description                                                                           |

|---------|--------------------------|---------------------------------------------------------------------------------------|

| 0x0059  | SCP_CONTROL              | Post pre-kick-start mode of SCP communication                                         |

|         |                          | Bits 2 1 0                                                                            |

|         |                          | 0 0 => I2C Master (Supported for firmware versions V01, V03 only)                     |

|         |                          | 0 0 1 => SPI Master (Supported for firmware versions V01, V03 only)                   |

|         |                          | 1 0 0 => I2C Slave                                                                    |

|         |                          | 1 0 1 => SPI Slave                                                                    |

|         |                          | Default: 0x00000000                                                                   |

| 0x005D  | PLL1_CUSTOM_CONFIG2      | Read only                                                                             |

| 0X003D  | 1 EE1_00010W_00W102      | ADC, DAC clock.                                                                       |

| 0x005E  | CLKMGR2_CUSTOM_CONFIG0   | Reserved                                                                              |

| 0x005E  | CLKMGR2_CUSTOM_CONFIG1   | Read only                                                                             |

| 0.00031 | CERMON2_COSTOM_CONFIGT   | S/PDIF Rx clock.                                                                      |

| 0,,0000 | CLIMACDO CLISTOM CONFICO |                                                                                       |

| 0x0060  | CLKMGR2_CUSTOM_CONFIG2   | Read only                                                                             |

| 0.000   | ADO HOED MODES           | SRC clock.                                                                            |

| 0x006D  | ADC_USER_MODES           | Setting of ADC_USER_MODE. Bits [18:9] can be changed during runtime.                  |

|         |                          | Bits 0:3 ADC_ENABLE for ADCs                                                          |

|         |                          | 1 Enable                                                                              |

|         |                          | 0 Disable                                                                             |

|         |                          | Bit 4                                                                                 |

|         |                          | 1 Enables single-ended operation for all ADCs                                         |

|         |                          | 0 Differential operation for all ADCs                                                 |

|         |                          | Bit 5:8 Reserved                                                                      |

|         |                          | Bits 9:13 MUX_SELECT_CH2-ADC                                                          |

|         |                          | 0x01 AIN2A                                                                            |

|         |                          | 0x02 AIN3A                                                                            |

|         |                          | 0x04 AIN4A                                                                            |

|         |                          | 0x08 AIN5A                                                                            |

|         |                          | Ox10 AIN6A                                                                            |

|         |                          | Bits 14:18 MUX_SELECT_CH3-ADC                                                         |

|         |                          | 0x01- AIN2B                                                                           |

|         |                          | 0x02- AIN3B                                                                           |

|         |                          | 0x04- AIN4B                                                                           |