CS4953x4/CS4970x4 32-bit Audio DSP Family

# CS4953x4/CS4970x4

System Designer's Guide

#### **Contacting Cirrus Logic Support**

For all product questions and inquiries, contact a Cirrus Logic Sales Representative. To find the one nearest you, go to www.cirrus.com.

#### IMPORTANT NOTICE

"Preliminary" product information describes products that are in production, but for which full characterization data is not yet available.

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, the Cirrus Logic logo designs, DSP Composer, Cirrus Extra Surround, Cirrus Original Multichannel Surround, and Cirrus Original Surround are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks or service marks of their respective owners.

Dolby, Dolby Digital, Dolby Headphone, Dolby Virtual Speaker, AC-3, and Pro Logic are registered trademarks of Dolby Laboratories, Inc. AAC, Dolby Headphone2, Dolby Virtual Speaker2, and Dolby Digital Surround EX are trademarks of Dolby Laboratories, Inc. Supply of an implementation of Dolby technology does not convey a license nor imply a right under any patent, or any other industrial or intellectual property right of Dolby Laboratories, to use the implementation in any finished enduser or ready-to-use final product. It is hereby notified that a license for such use is required from Dolby Laboratories.

DTS and DTS Digital Surround are registered trademarks of the Digital Theater Systems, Inc. DTS-ES, DTS-ES 96/24, DTS Neo:6, DTS 96/24 are trademarks of the Digital Theater Systems, Inc. It is hereby notified that a third-party license from DTS is necessary to distribute software of DTS in any finished end-user or ready-to-use final product.

THX® is a registered trademark of Lucasarts Entertainment Company Corporation.

Re-equalization is a trademark of Lucasfilm, Ltd.

SRS is a registered trademark of SRS Labs, Inc. Purchaser of CS4953x4/CS4970x4 must sign a license for use of the chip and display of the SRS Labs trademarks. Any products incorporating the CS4953x4/CS4970x4 must be sent to SRS Labs for review. The SRS symbol is a trademark of SRS Labs, Inc. in the United States and selected foreign countries. Neither the purchase of the CS4953x4/CS4970x4, nor the corresponding sale of audio enhancement equipment conveys the right to sell commercialized recordings made with any SRS technology/solution. SRS Labs requires all set makers to comply with all rules and regulations as outlined in the SRS Trademark Usage Manual.

Intel is a registered trademark of Intel Corporation.

Motorola and SPI are registered trademarks of Motorola, Inc.

I2C is a trademark of Philips Semiconductor Corp.

HDMI is a trademark of HDMI Licensing.

BLU-RAY and BLU-RAY DISC are trademarks of SONY KABUSHIKI KAISHA CORPORATION.

Microsoft and Windows XP are registered trademarks of Microsoft Corporation.

## Contents

| Contents                                                       |          |

|----------------------------------------------------------------|----------|

| Figures                                                        |          |

| Tables                                                         |          |

| Preface                                                        | P-1      |

| P.1 Introduction to CS4953x4/CS4970x4 System Designer's Guide  |          |

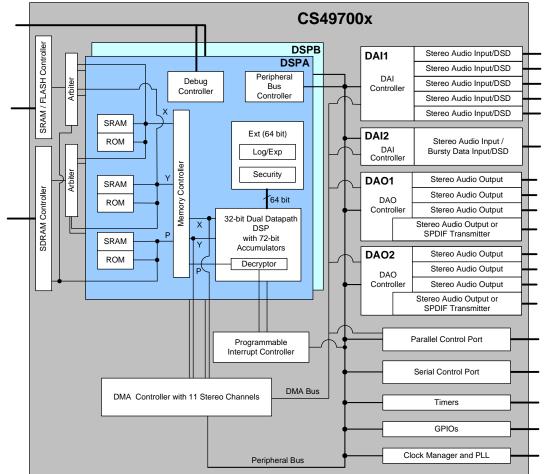

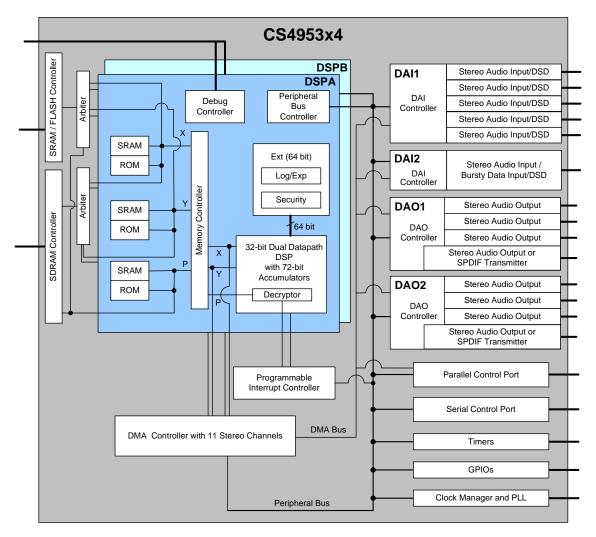

| P.2 Overview of the CS4953x4/CS4970x4 DSP                      |          |

| P.2.1 Chip Features                                            |          |

| P.3 CS4953x4/CS4970x4 Chip Functional Overview                 |          |

| P.3.1 DSP Core                                                 | P-4      |

| P.3.2 Security Extension module                                | P-4      |

| P.3.3 Debug Controller (DBC)                                   | P-4      |

| P.3.4 Digital Audio Output (DAO1, DAO2) Controller             | P-4      |

| P.3.5 Digital Audio Input (DAI1) Controller                    | P-4      |

| P.3.6 Compressed Data Input / Digital Audio Input (DAI2) Contr | ollerP-4 |

| P.3.7 Direct Stream Digital (DSD) Controller                   | P-5      |

| P.3.8 General Purpose I/O                                      |          |

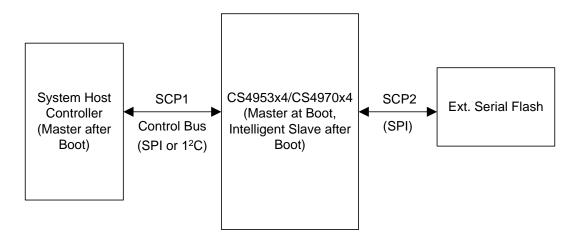

| P.3.9 Serial Control Ports (SPI™ or I2C™ Standards)            | P-5      |

| P.3.10 SDRAM Controller                                        |          |

| P.3.11 DMA Controller                                          |          |

| P.3.12 Timers                                                  |          |

| P.3.13 Clock Manager and PLL                                   |          |

| P.3.14 Programmable Interrupt Controller                       |          |

| P.4 Firmware Overview                                          |          |

| P.4.1 Robust DSP Manager Firmware API                          |          |

| P.4.2 DSP Condenser                                            |          |

| P.5 CS40700x Pin Descriptions                                  |          |

| P.5.1 Power and Ground                                         |          |

| P.5.1.1 Power                                                  |          |

| P.5.1.2 Ground                                                 |          |

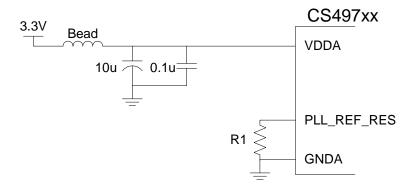

| P.5.1.3 Decoupling<br>P.5.2 PLL Filter                         |          |

| P.5.2.1 Analog Power Conditioning                              |          |

| P.5.2.2 PLL                                                    |          |

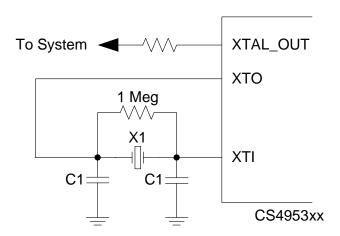

| P.5.3 Clocking                                                 |          |

| P.5.4 Control                                                  | P-10     |

| P.5.4.1 Operational Mode                                       |          |

| P.6 CS4970x4 Pin Assignments                                   |          |

| P.7 CS4953x4 Pin Assignments                                   | P-19     |

| Chapter 1. Operational Modes                                   | 1-1      |

| 1.1 Overview                                                   |          |

| 1.1.1 Supported Serial Flash Devices                           |          |

| 1.2 Operational Mode Selection                                 |          |

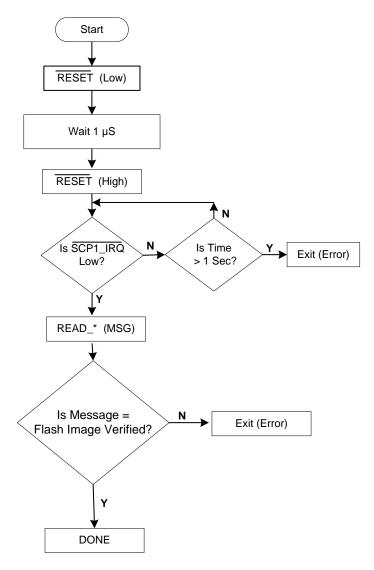

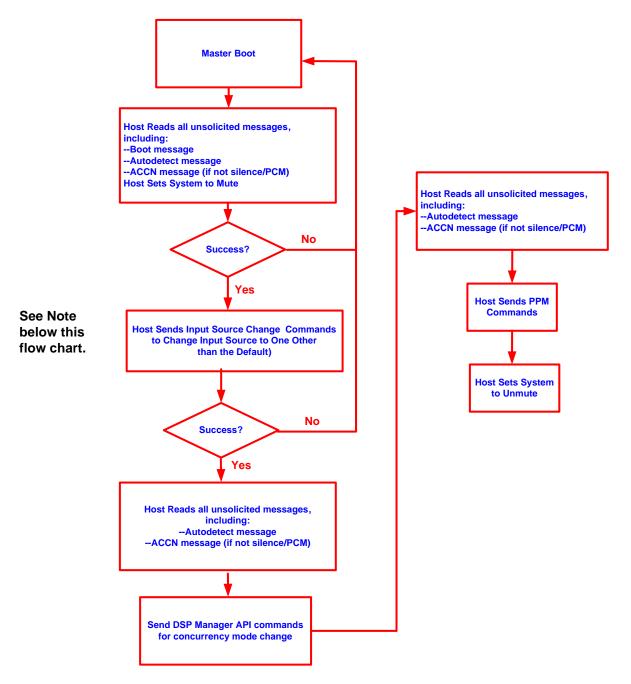

| 1.3 Booting the DSP in Master Boot Mode                        |          |

| 1.3.1 Performing a Master Boot                                 |          |

| 1.3.1.1 Master Boot Protocol                                   |          |

| 1.3.1.2 Messages Read from CS4953x4/CS4970x4                   |          |

| Chapter 2. Serial Communication Mode             | 2-1  |

|--------------------------------------------------|------|

| 2.1 Introduction                                 |      |

| 2.2 Communication Using the Serial Control Port  |      |

| 2.3 Serial Control Port Configuration            |      |

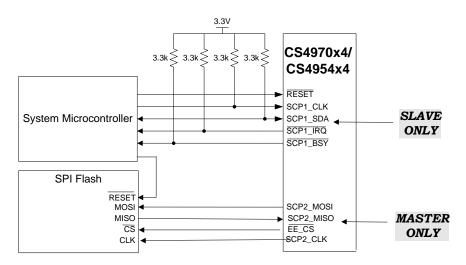

| 2.4 SPI Port                                     |      |

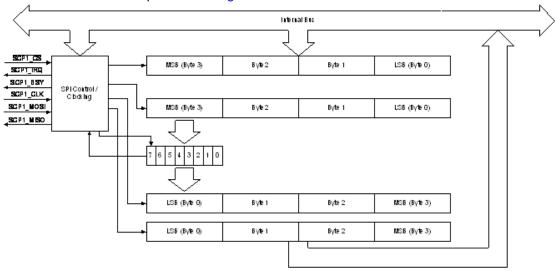

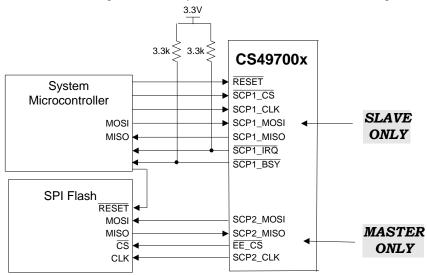

| 2.4.1 SPI System Bus Description                 |      |

| 2.4.2 SPI Bus Dynamics                           |      |

| 2.4.2.1 SCP1 BSY Behavior                        |      |

| 2.4.3 SPI Messaging                              |      |

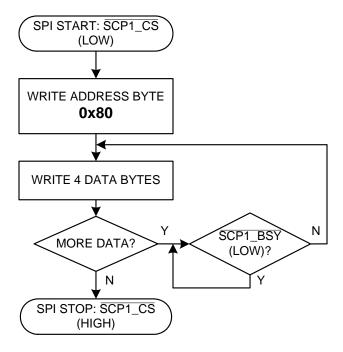

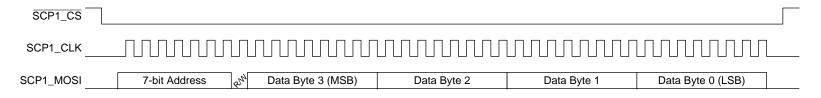

| 2.4.3.1 Performing a Serial SPI Write            |      |

| 2.4.3.2 SPI Write Protocol                       |      |

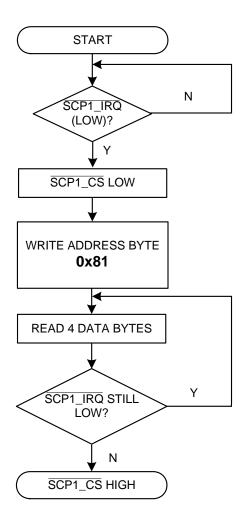

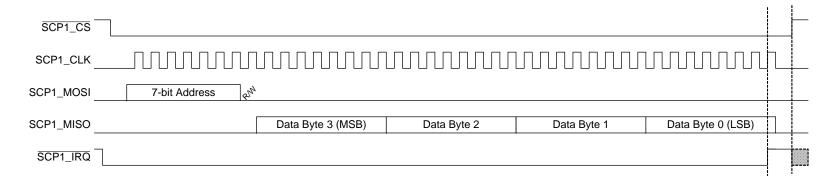

| 2.4.3.3 Performing a Serial SPI Read             |      |

| 2.4.3.4 SPI Read Protocol                        |      |

| 2.4.3.5 SCP1_IRQ Behavior                        |      |

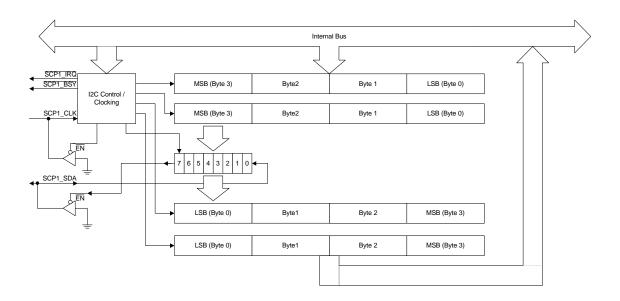

| 2.5 I2C Port                                     |      |

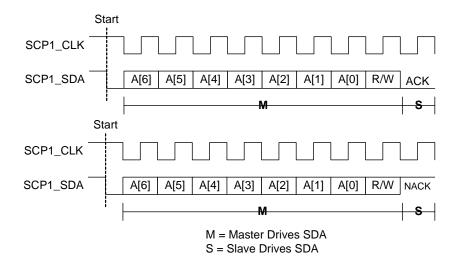

| 2.5.1 I <sup>2</sup> C System Bus Description    | 2-10 |

| 2.5.2 I <sup>2</sup> C Bus Dynamics              |      |

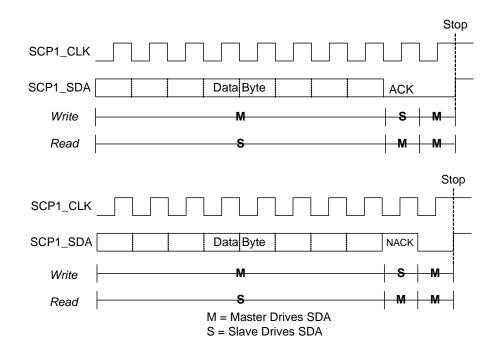

| 2.5.3 I2C Messaging                              |      |

| 2.5.3.1 SCP1 BSY Behavior                        |      |

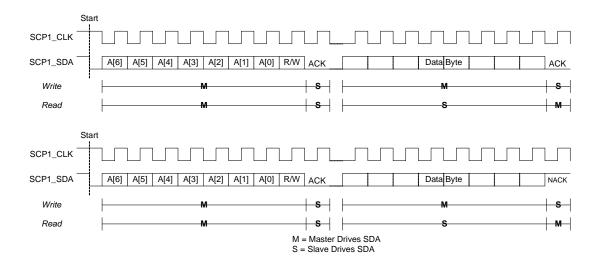

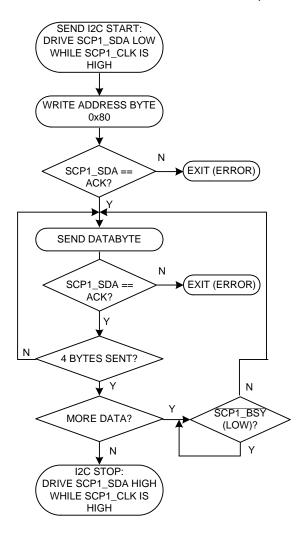

| 2.5.3.2 Performing a Serial I2C Write            |      |

| 2.5.3.3 I2C Write Protocol                       |      |

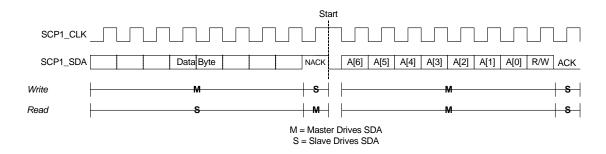

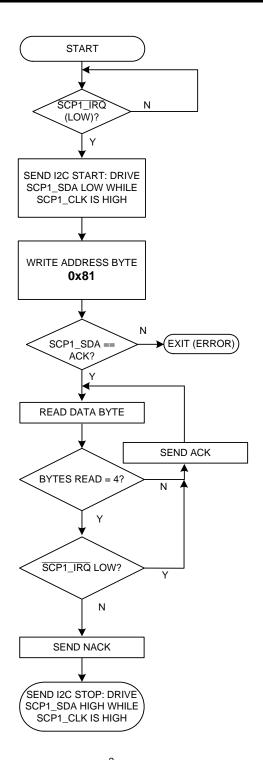

| 2.5.3.4 Performing a Serial I2C Read             |      |

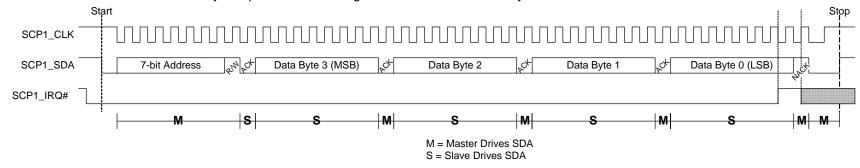

| 2.5.3.5 I2C Read Procedure                       |      |

| 2.5.3.6 SCP1_IRQ Behavior                        | 2-20 |

| Chapter 3. Audio Input Interfaces                |      |

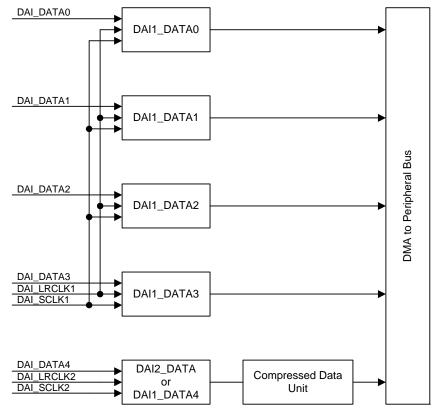

| 3.2.1 DAI Pin Description                        |      |

| 3.2.2 Supported DAI Functional Blocks            |      |

| 3.2.3 BDI Port                                   |      |

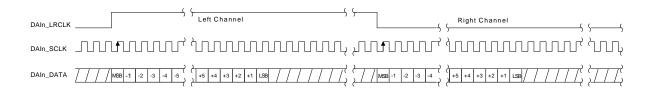

| 3.2.4 Digital Audio Formats                      |      |

| 3.2.4.1 I2S Format                               |      |

| 3.2.4.1 123 Format                               |      |

| 3.3 DAI Hardware Configuration                   |      |

| 3.3.1 DAI Hardware Naming Convention             |      |

| 3.4 Digital Audio Input Port Description         |      |

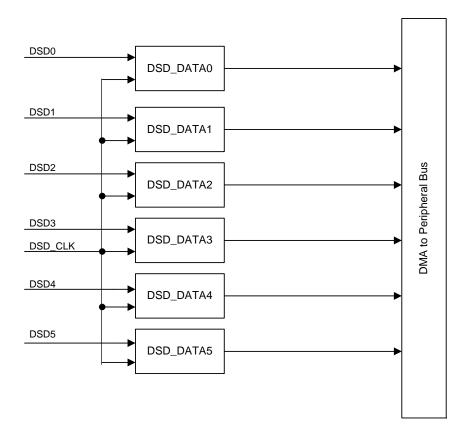

| 3.4.1 DSD Pin Description                        |      |

| 3.4.2 Supported DSD Functional Blocks            |      |

| 3.4.2 Supported DSD Functional Blocks            | 3-1  |

| Chapter 4. Audio Output Interface                |      |

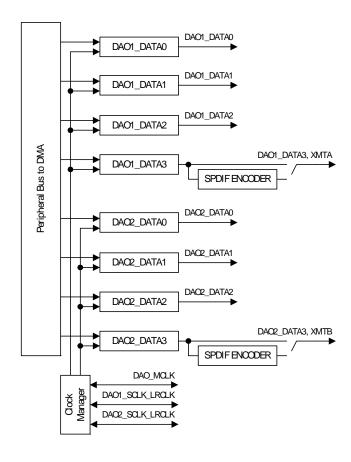

| 4.1 Introduction                                 |      |

| 4.2 Digital Audio Output Port Description        |      |

| 4.2.1 DAO Pin Description                        |      |

| 4.2.2 Supported DAO Functional Blocks            |      |

| 4.2.3 DAO Interface Formats                      |      |

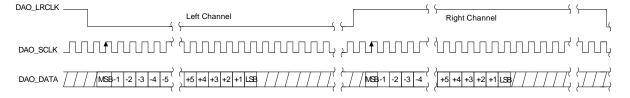

| 4.2.3.1 I2S Format                               |      |

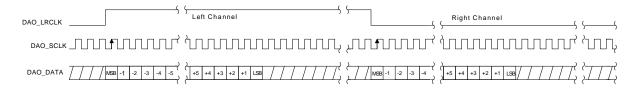

| 4.2.3.2 Left-Justified Format                    |      |

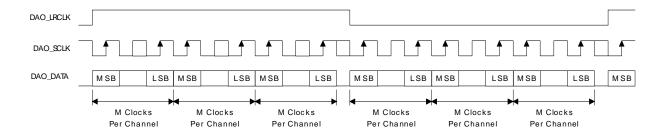

| 4.2.3.3 One-line Data Mode Format (Multichannel) |      |

| 4.2.4 DAO Hardware Configuration                 |      |

| 4.2.5 DAO Hardware Naming Convention             |      |

|                                                  |      |

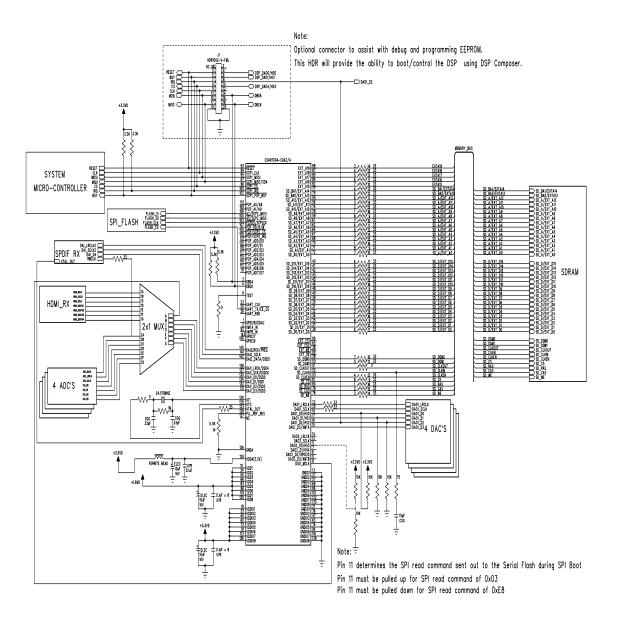

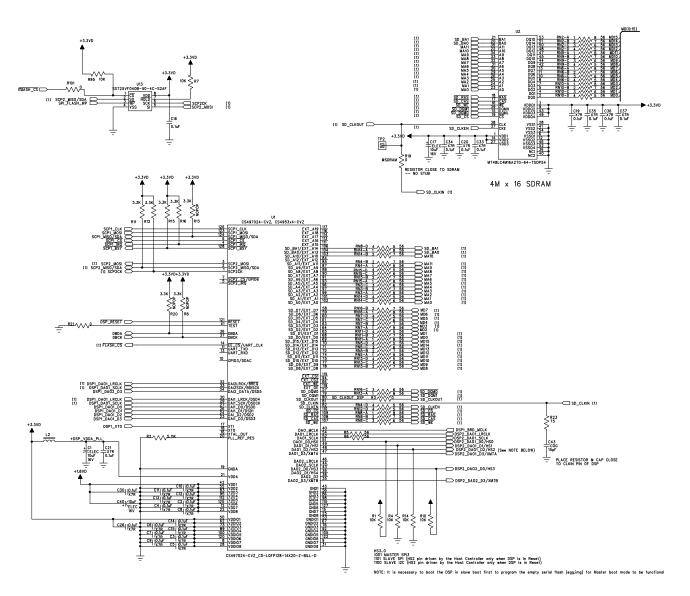

| Chapter 5. External Memory Interfaces                           | 5-1  |

|-----------------------------------------------------------------|------|

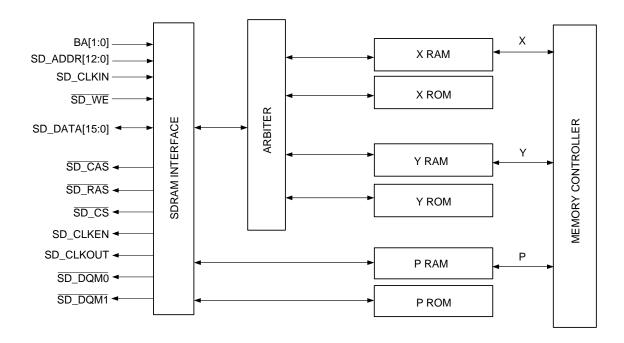

| 5.1 SDRAM Controller                                            |      |

| 5.1.1 SDRAM Controller Interface                                |      |

| 5.1.2 SDRAM Interface Signals                                   |      |

| 5.1.3 Configuring SDRAM Parameters                              |      |

| 5.2 SPI Flash Interface                                         |      |

|                                                                 |      |

| Chapter 6. System Design Requirements for SPDIF and             |      |

| HDMI™ Technology Interfaces                                     | 6-1  |

| 6.1 Introduction                                                | 6-1  |

| 6.1.1 Designing a SPDIF Input Interface                         | 6-1  |

| 6.1.1.1 SPDIF Clocking                                          | 6-1  |

| 6.1.2 Designing an HDMI Input Interface                         | 6-1  |

| 6.1.2.1 HDMI Clocking                                           |      |

| 6.1.2.2 Decoding Stream Types Over HDMI                         |      |

| 6.1.3 Other System Design Considerations                        | 6-2  |

| Chapter 7. Overview of Common Firmware Modules                  | 7-1  |

| 7.1 Introduction                                                |      |

| 7.2 CS4953x4/CS4970x4 Firmware                                  |      |

| 7.2.1 Firmware Modules                                          |      |

| 7.2.2 Overlay Architecture                                      | 7-1  |

| 7.3 Firmware Messaging                                          |      |

| 7.3.1 Communication Overview                                    |      |

| 7.3.2 Writing to the DSP                                        | 7-2  |

| 7.3.3 Solicited Read                                            | 7-3  |

| 7.3.4 Unsolicited Read                                          | 7-3  |

| 7.3.5 Index Configuration                                       | 7-4  |

| 7.3.6 Unsolicited Messages from DSP to the Host Microcontroller | 7-4  |

| 7.3.7 DSP_AUTODETECT_MSG                                        | 7-4  |

| 7.3.8 DSP_LAST_ACCN_MSG                                         | 7-5  |

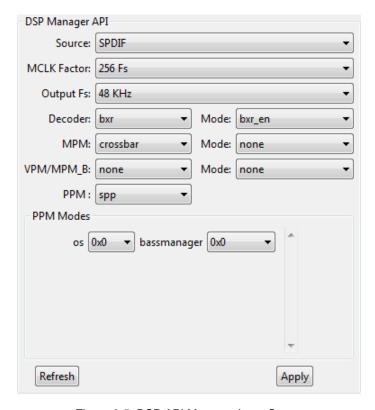

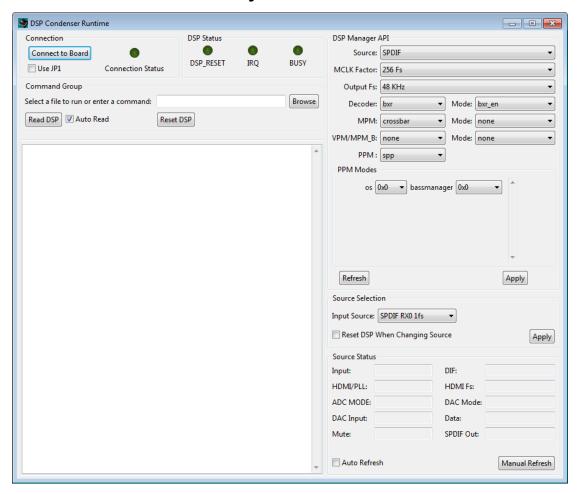

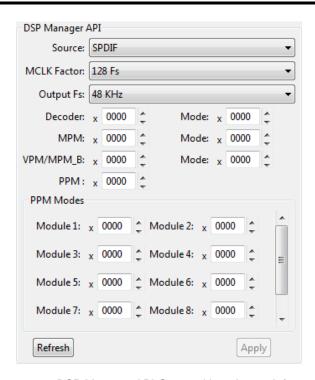

| 7.4 CS4953x4/CS4970x4 DSP Manager API Description               | 7-6  |

| 7.4.1 Microcontroller Interface (API)                           | 7-6  |

| 7.4.2 DSP_CFG_xxx Registers                                     | 7-7  |

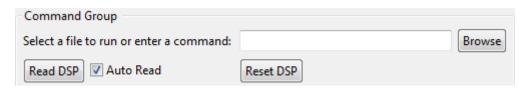

| 7.4.2.1 Using DSP Condenser to Change/Load Firmware Modules     | 7-10 |

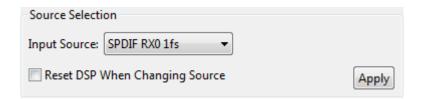

| 7.4.2.2 Using DSP Condenser to Change the Audio Input Source    |      |

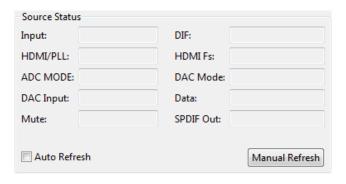

| 7.4.3 Status Registers                                          |      |

| 7.5 Legacy API Still in Use                                     |      |

| 7.5.1 Legacy Audio Manager                                      |      |

| 7.6 OS Firmware Module                                          |      |

| 7.6.1 Overview                                                  |      |

| 7.6.2 OS-A and OS-B Module Manager                              |      |

| 7.6.3 Other DSP Audio Manager Registers                         | 7-17 |

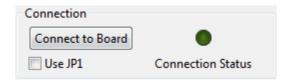

| Chapter 8. DSP Condenser                                        | 8-1  |

| 8.1 Overview                                                    |      |

| 8.1.1 Purpose of DSP Condenser                                  |      |

| 8.2 Development Flow                                            |      |

| 8.3 Elements of a Project                                       |      |

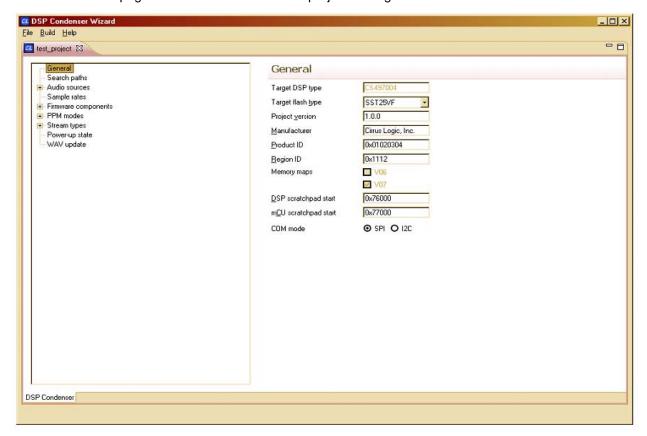

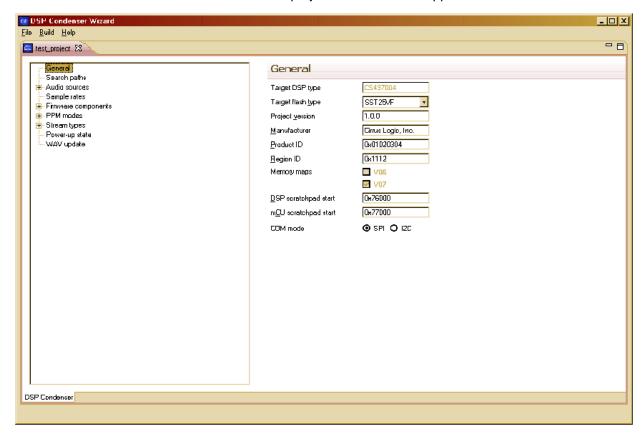

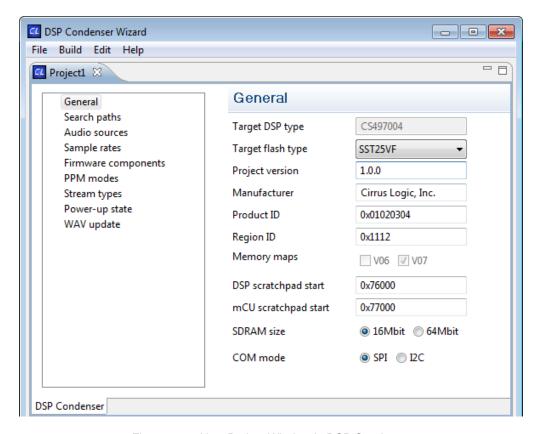

| 8.3.1 General Page                                              |      |

|                                                                 |      |

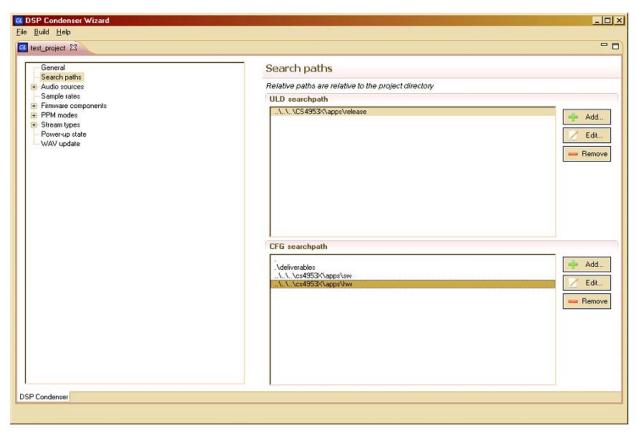

|     | 8.3.2 Search paths Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8-5  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

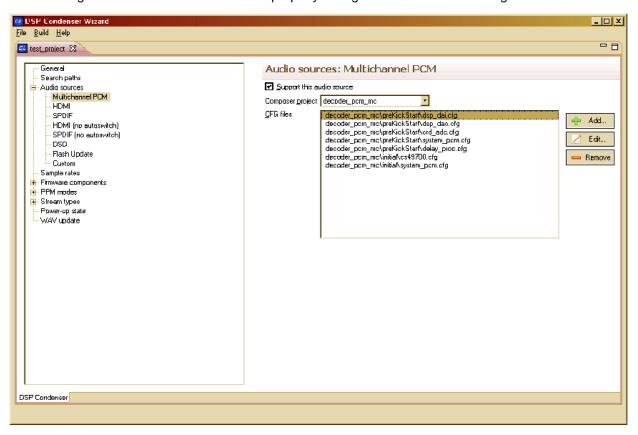

|     | 8.3.3 Audio sources Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-6  |

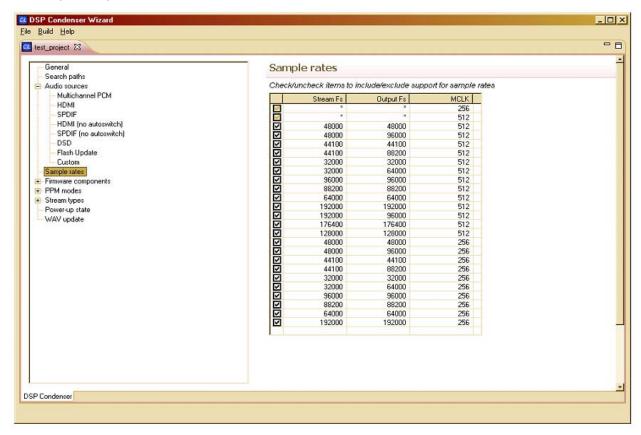

|     | 8.3.4 Sample rates Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8-7  |

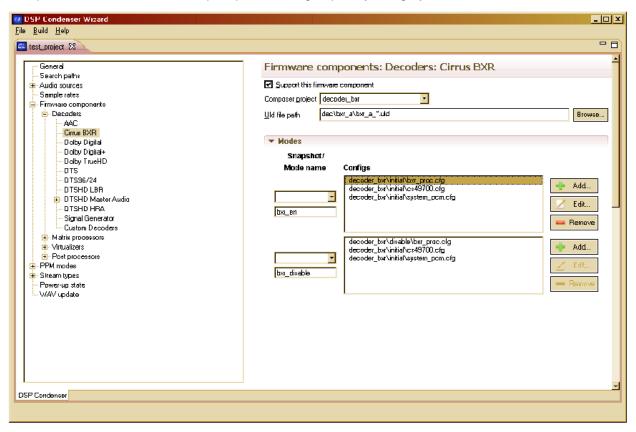

|     | 8.3.5 Firmware components Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8-8  |

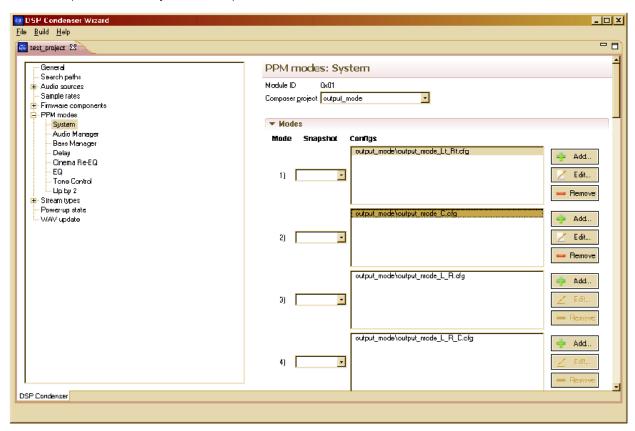

|     | 8.3.6 PPM modes Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-9  |

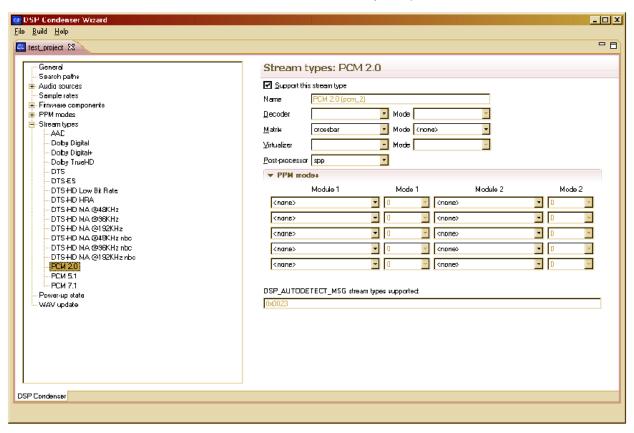

|     | 8.3.7 Stream types Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8-10 |

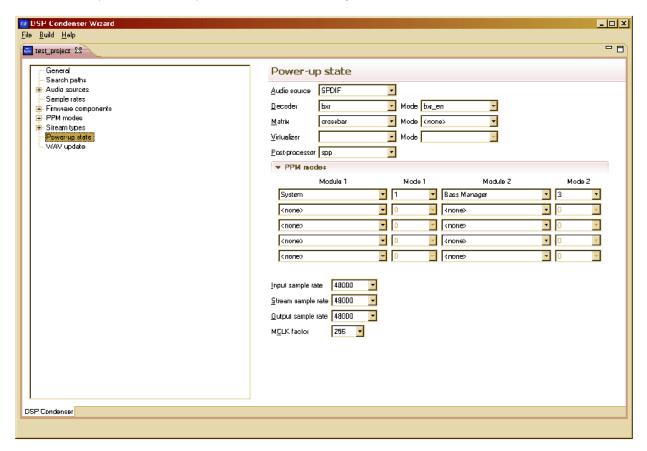

|     | 8.3.8 Power-up state Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

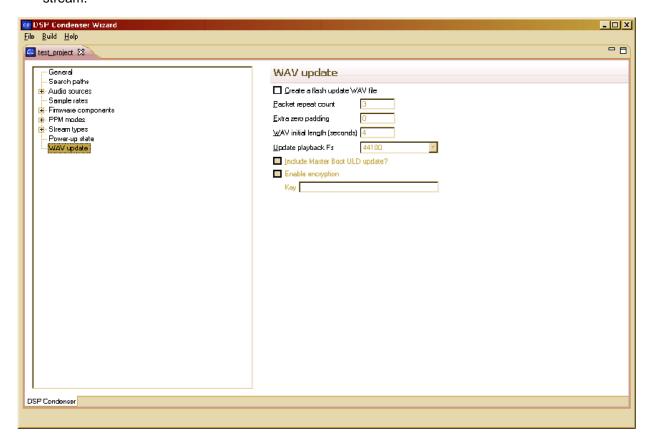

|     | 8.3.9 WAV update Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

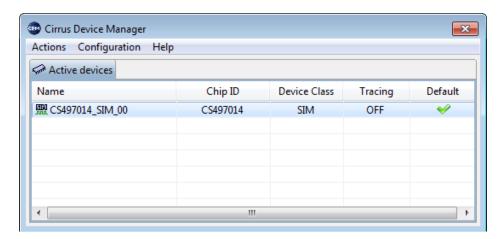

|     | 8.4 Hardware and Software Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|     | 8.4.1 Hardware requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|     | 8.4.2 Software requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

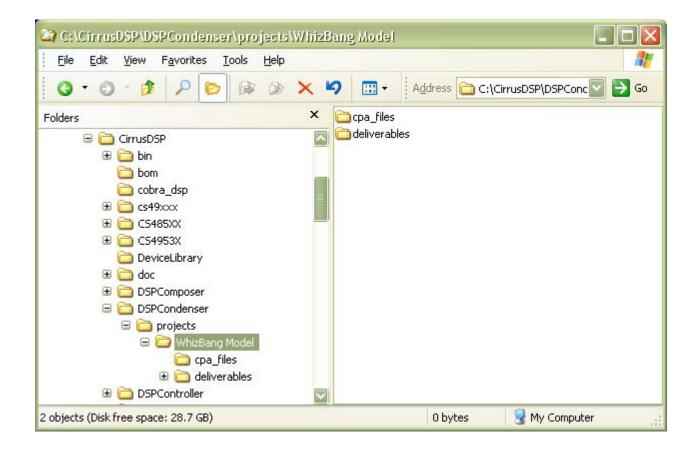

|     | 8.5 Creating a Condenser Project using a Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

|     | 8.5.1 Using the Wizard to Create a Project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

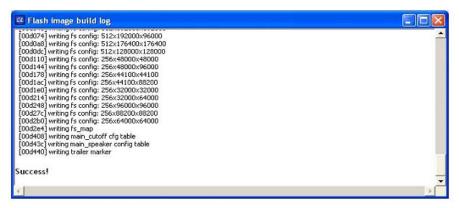

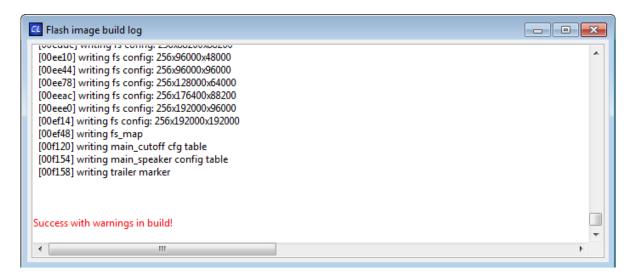

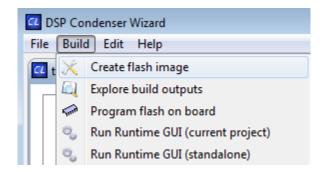

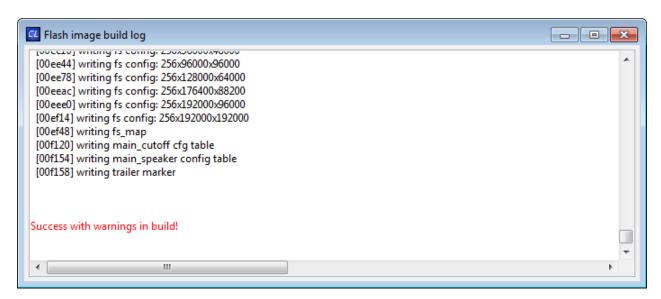

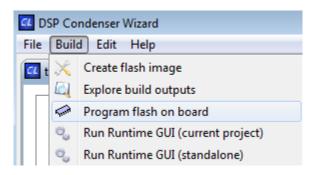

|     | 8.6 Creating a Flash Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

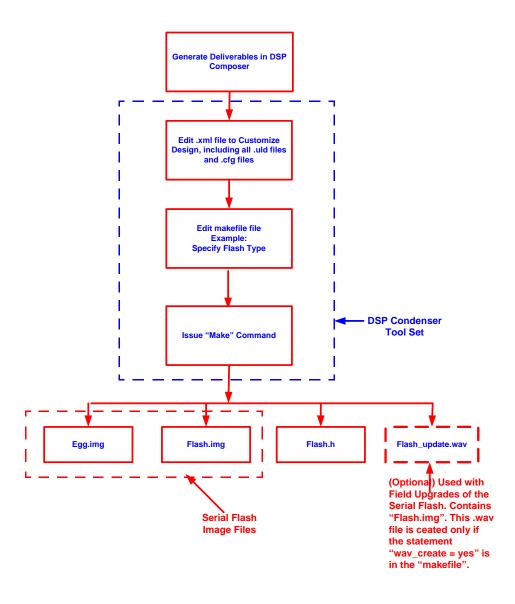

|     | 8.6.1 How to create an image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

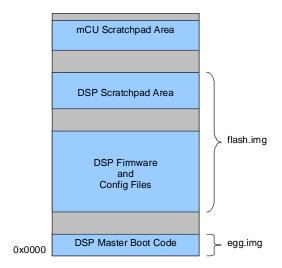

|     | 8.6.2 What Does the Image Contain?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

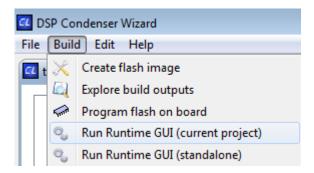

|     | 8.7 Using DSP Condenser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|     | 8.7.1 How to use DSP Composer with DSP Condenser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|     | 8.7.1.1 Best Practices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|     | 8.7.1.2 Creating Projects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

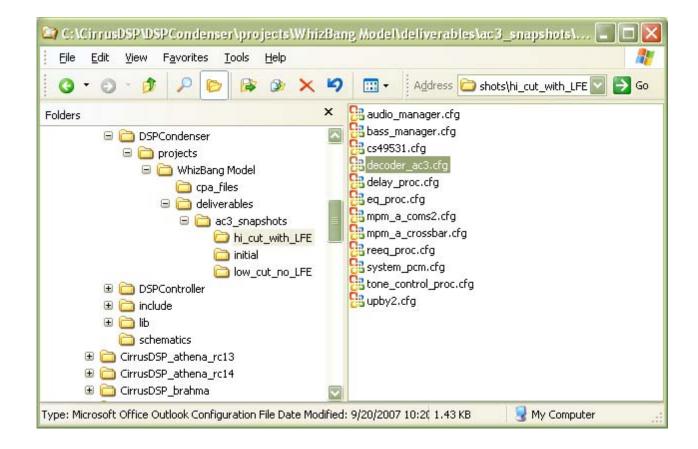

|     | 8.7.2 Capturing Snapshots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|     | 8.8 Creating a Flash Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

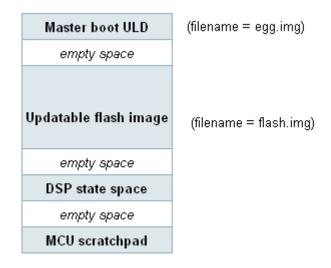

|     | 8.8.1 SPI Flash Image Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|     | 8.8.1.1 Master Boot Image (egg.img)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|     | 8.8.1.2 Updatable Flash Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|     | 8.8.1.3 DSP State Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|     | 8.8.1.4 Microcontroller Unit (MCU) Scratchpad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|     | 8.8.2 Creating a Serial Flash Image Automatically                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |